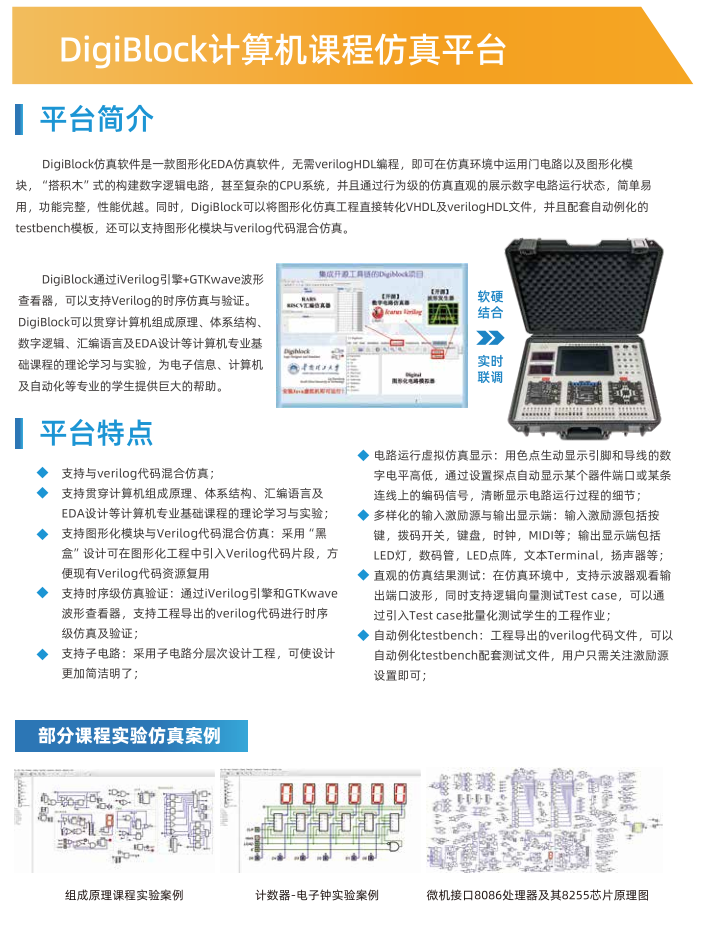

DigiBlock计算机课程仿真平台

■ DigiBlock是一款图形化的设计EDA软件,无需verilogHDL编程。

■ “搭积木”式的构建数字逻辑电路,甚至复杂的CPU系统。

■ 贯穿计算机组成原理、体系结构、汇编语言及EDA设计等计算机专业基础课程的理论学习与实验。

■ 支持时序级仿真验证:通过iVerilog引擎和GTKwave波形查看器,支持工程导出的verilog代码进行时序级仿真及验证

■ 包括组合逻辑,时序逻辑,状态机等数字逻辑电路实验,运算器(加减法,乘除法,浮点),存储器,CPU(ARMv8/RISCV)等

DigiBlock是一款图形化的设计EDA软件,无需verilogHDL编程,即可在仿真环境中运用门电路以及图形化模块,“搭积木”式的构建数字逻辑电路,甚至复杂的CPU系统,并且通过行为级的仿真直观的展示数字电路运行状态,简单易用,功能完整,性能优越。同时,DigiBlock可以将图形化仿真工程直接转化VHDL及verilogHDL文件,并且配套自动例化的testbench模板,还可以支持图形化模块与verilog代码混合仿真。进一步,DigiBlock通过开源的iVerilog引擎+GTKwave波形查看器,可以支持Verilog的时序仿真与验证。DigiBlock可以贯穿计算机组成原理、体系结构、汇编语言及EDA设计等计算机专业基础课程的理论学习与实验,为电子信息、计算机及自动化等专业的学生提供巨大的帮助。

DigiBlock仿真软件部分实验案例

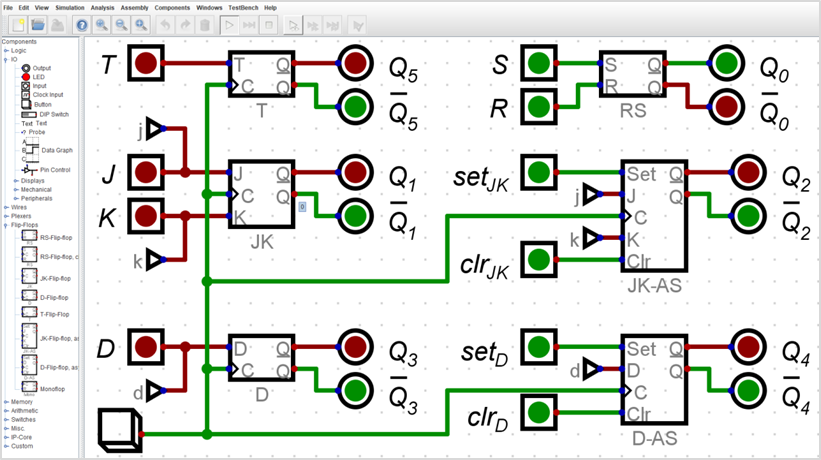

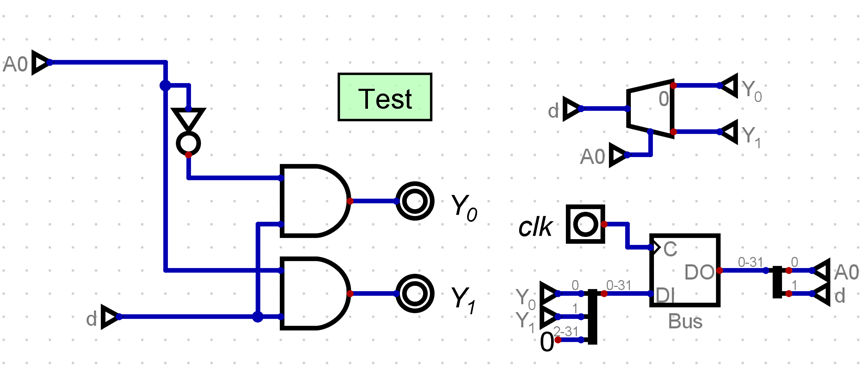

数字逻辑-门电路构建1-2多路选择器的实验

与门和反相器构成1-2多路选择器的实验,选择基本部件,根据1-2多路选择器的真值表,选择与门和反相器在Digiblock中的布局如下图所示。添加输入,输出端口和连线,构成门电路。

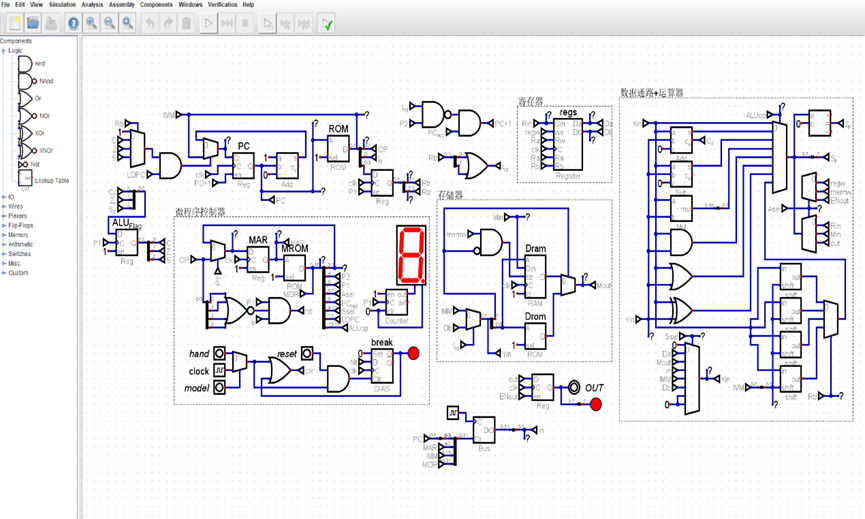

组成原理-微程序控制器第二阶段实验

实验在最小版本指令集(NOP/HLT/JUMP)基础上,扩充以下三类指令:存储器赋值指令:MOV寄存器间赋值/SET寄存器立即数赋值;IO读写指令:IN读端口/OUT写端口;存储器操作指令:LAD读存储器/STO写存储器,POP堆栈出栈/PUSH堆栈入栈(注:此处堆栈是以存储器为物理载体,通用寄存器为“指针”的软堆栈)

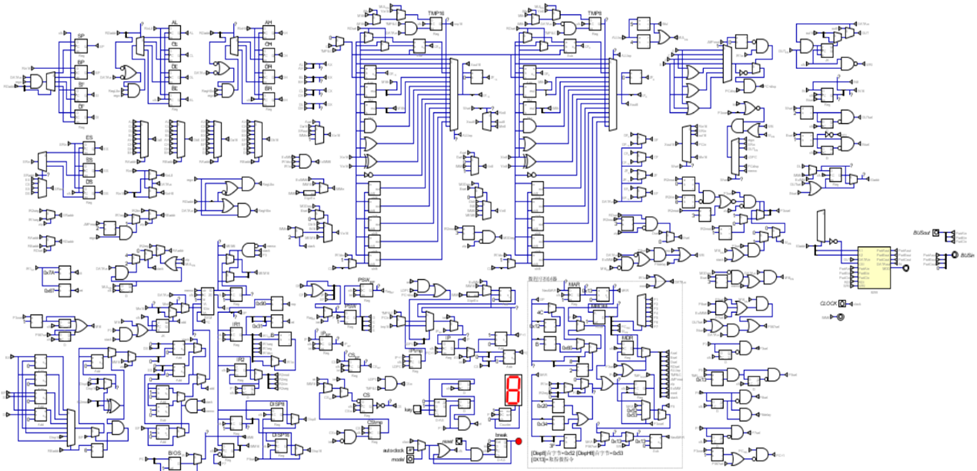

微机接口-微控制器8255实验

实验完成将寄存器AL的值赋予输出端口PA,然后从8255端口B读入数据,再通过端口C输出,所有读入数据均由实验箱面板的拨码开关提供,所有输出数据都显示在实验箱面板的LED矩阵上。图中,8255芯片子电路的结构如下图所示,8086CPU通过编程,实现对PA,PB及PC这三个8位端口的访问,实现了8086处理器的IO端口的扩展。

其它实验案例

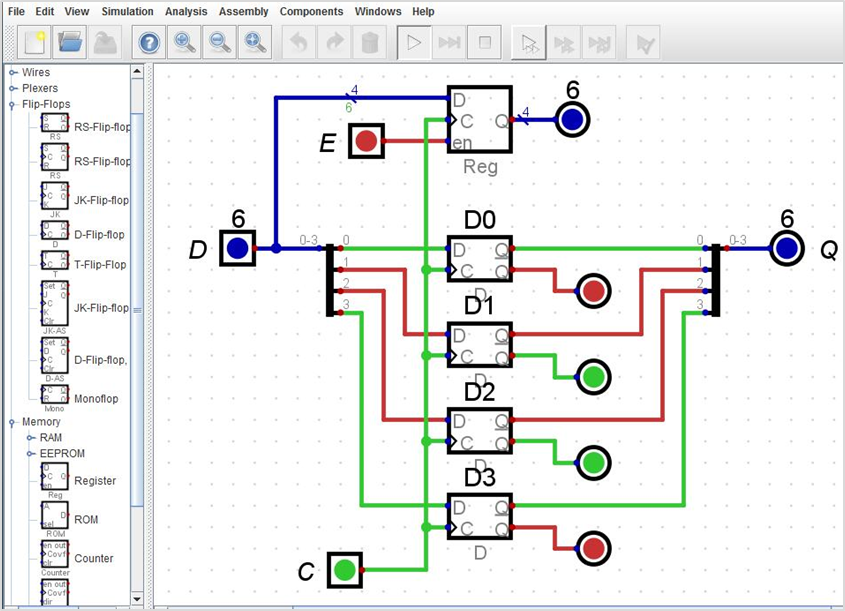

(注:图中所有触发器的任意端口均可设置取反,处理数据的长度均可以设置)

时序逻辑的特点——存储数据:寄存器及其D触发器的等效电路

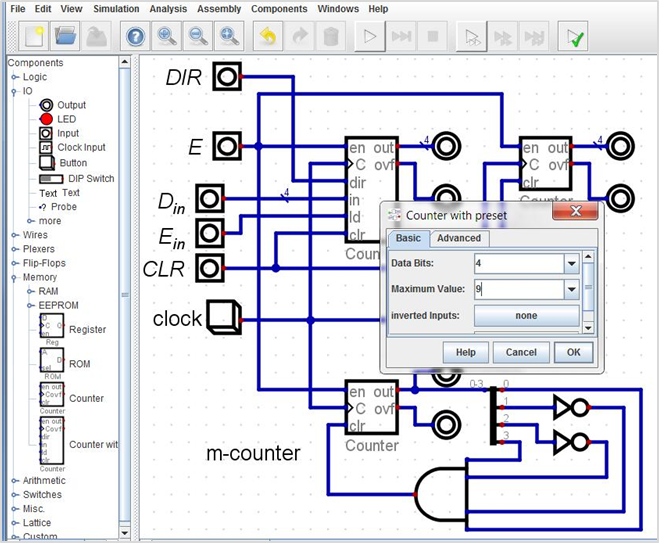

计数器及带加载、置位和清零功能的计数器(注:m进制设置Max值为m-1)

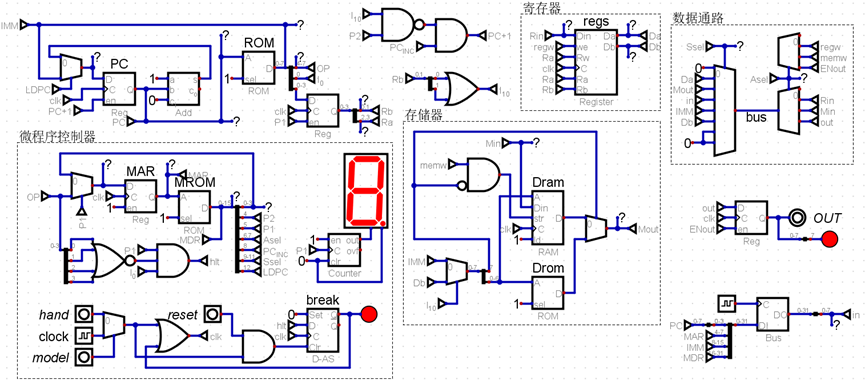

组成原理实验案例

(注:图示控制器实验和软硬联调案例)